# Bias stress stability of zinc-tin-oxide thin-film transistors with $AI_2O_3$ gate dielectrics

J. Triska, J. F. Conley, Jr.,<sup>a)</sup> R. Presley, and J. F. Wager

School of Electrical Engineering and Computer Science, Oregon State University, Corvallis, Oregon 97333-5501

(Received 23 March 2010; accepted 24 May 2010; published 6 July 2010)

The bias stability of zinc-tin-oxide (ZTO) thin-film transistors (TFTs) with either Al<sub>2</sub>O<sub>3</sub> gate dielectrics deposited via atomic layer deposition (ALD) or SiO<sub>2</sub> gate dielectrics deposited via plasma-enhanced chemical vapor deposition (PECVD) was compared. Both device types showed incremental mobility  $\geq 11 \text{ cm}^2/\text{V}$  s, subthreshold slopes <0.4 V/dec, and  $I_{ON}/I_{OFF}$  ratios of ~10<sup>7</sup>. During repeated  $I_D$ - $V_{GS}$  sweeping, both device types showed positive parallel shift of the turn-on voltage ( $V_{ON}$ ) without significant degradation of subthreshold slope or mobility, consistent with electron trapping without creation of new traps. A smaller  $V_{ON}$  shift was observed in the SiO<sub>2</sub>/ZTO devices. In an effort to improve the bias stress stability of the Al<sub>2</sub>O<sub>3</sub>/ZTO devices, the impact of ALD temperature, plasma exposure of the Al<sub>2</sub>O<sub>3</sub>, and the addition of an interfacial PECVD SiO<sub>2</sub> capping layer were investigated. The positive bias stress stability of the Al<sub>2</sub>O<sub>3</sub>/ZTO TFTs was found to be relatively unaffected by the Al<sub>2</sub>O<sub>3</sub> ALD temperature, degraded with plasma exposure, and improved by the addition of a thin (~3 nm) PECVD SiO<sub>2</sub> interfacial layer between the Al<sub>2</sub>O<sub>3</sub> dielectric and the ZTO channel. These results point to the vicinity of the Al<sub>2</sub>O<sub>3</sub>/ZTO interface as the dominant source of charge trapping. © *2010 American Vacuum Society*. [DOI: 10.1116/1.3455494]

# I. INTRODUCTION

Recent reports of thin-film transistors (TFTs) and transparent TFTs based on ZnO (Refs. 1-4) and amorphous oxide semiconductor (AOS) channel materials such as InGaZnO (IGZO) and ZnSnO (ZTO) have generated interest for active matrix organic light emitting diode (AMOLED) display applications.<sup>5–14</sup> Because AMOLED displays are emissive and current driven, high mobility is important and the stability of the TFT current drivers is critical for high visual quality, as shifts in the threshold voltage  $(V_{th})$  during operation will affect pixel brightness. TFT technology is currently dominated by amorphous hydrogenated silicon (a-Si:H), yet this material exhibits several drawbacks. Perhaps most significantly, a-Si:H mobility is limited to approximately  $1 \text{ cm}^2/\text{V}$  s. Another major drawback is that significant irreversible instabilities occur during light exposure and bias stressing,<sup>15–17</sup> which must be taken into account when designing circuits, as the devices age during operation.<sup>18</sup> These drawbacks may limit the use of a-Si:H in AMOLED display applications.

AOS materials, on the other hand, exhibit mobilities from 5 to >50 cm<sup>2</sup>/V s even though disordered. This has been explained by the fact that conduction in these materials is through symmetric metal *ns* orbitals, rather than directed covalent  $sp^3$  orbitals.<sup>1</sup> It has been proposed that this bonding arrangement may make AOS materials inherently more stable than *a*-Si:H.<sup>19</sup> ZTO is a promising AOS that has a relatively high mobility of >10 cm<sup>2</sup>/V s at low processing temperatures.<sup>5,6,14,20-22</sup> Before it can be considered as a replacement for *a*-Si:H as a current driver for AMOLED dis-

plays, the operational stability of ZTO-based TFTs must be understood. There have been relatively few studies to date assessing the reliability of ZTO devices. Most reports on ZTO TFTs have used SiO<sub>2</sub> or AlTiO<sub>x</sub> (ATO) as the gate dielectric.<sup>14,20,23</sup> In this work, the initial operational stability as well as the long term positive constant voltage stress stability of ZTO TFTs with gate dielectrics consisting of either Al<sub>2</sub>O<sub>3</sub> deposited via atomic layer deposition (ALD), SiO<sub>2</sub> deposited via plasma-enhanced chemical vapor deposition (PECVD), or ALD Al<sub>2</sub>O<sub>3</sub> capped with a thin layer of PECVD SiO<sub>2</sub> were investigated.

## **II. EXPERIMENT**

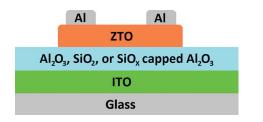

A cross-section of the staggered bottom-gate (SBG) TFTs used in this study is shown in Fig. 1. SBG TFTs with width to length  $(W/L) = 1000/100 \ \mu m$  were fabricated on indium tin oxide (ITO)-coated glass (Delta Technologies). First, a gate dielectric of either (i) 200 nm Al<sub>2</sub>O<sub>3</sub>, (ii) 100 nm SiO<sub>2</sub>, or (iii) 200 nm  $Al_2O_3$  capped with ~2-5 nm SiO<sub>2</sub> was blanket deposited on the ITO gate. ALD of Al<sub>2</sub>O<sub>3</sub> was performed at 200 °C (unless otherwise noted), using trimethylaluminum (TMA) and water as precursors. SiO<sub>2</sub> was deposited via PECVD at 400 °C using 2% silane (balanced in helium) and nitrous oxide as precursors. Next, using a shadow mask, an approximately 65 nm ZTO channel was deposited via rf sputtering at 5 mTorr working pressure, a 90/10 Ar/O<sub>2</sub> ratio, and, unless otherwise noted, 75 W of rf power. The Zn:Sn ratio is estimated to be roughly 2:1 based on the 2:1 Zn:Sn composition ration of the sputter target. Following the ZTO deposition, devices were annealed in air at 400 °C for 1 h (5 °C/min ramp rate). Finally, ~400 nm thick Al contacts were deposited by thermal evaporation and defined using a shadow mask.

<sup>&</sup>lt;sup>a)</sup>Electronic mail: jconley@eecs.oregonstate.edu

FIG. 1. (Color online) Schematic cross-section of a staggered bottom-gate TFT structure.

Electrical characterization was performed using an Agilent 4155C semiconductor parameter analyzer. Doublesweep  $I_D$ - $V_{GS}$  transfer curves were measured with  $V_{DS}$  held at +1 V using an integration time of 0.27 s. One doublesweep consisted of ramping  $V_{GS}$  from -5 to +20 V and then back to -5 in 0.25 V steps, with a sweep rate of approximately 0.25 V/s. All measurements were made inside a dark box at room temperature in atmosphere.  $V_{ON}$  was empirically defined as the onset of drain current in the log( $I_D$ )- $V_{GS}$  transfer curve.<sup>24,25</sup> Subthreshold slope (S) was defined as the maximum slope of log( $I_D$ )- $V_{GS}$  and was reported in units of V/dec of current. Following Hoffman,<sup>25</sup> incremental mobility,  $\mu_{inc}$ , was extracted from the  $I_D$ - $V_{GS}$  curve using

$$\mu_{\rm inc} = (\partial G_d / \partial V_{GS}) / (C_{\rm ox} W/L), \qquad (1)$$

where  $G_d$  is the conductance,  $C_{ox}$  is the geometric capacitance of the gate oxide, W is the width, and L is the length of the transistor. The maximum incremental mobility,  $\mu_{inc}(max)$ , is reported. Bias stressing was performed at room temperature in the dark with  $V_{GS}$ =+20 V and  $V_{DS}$ =+1 V. Stress was interrupted at approximately logarithmic time intervals to measure  $I_D$ - $V_{GS}$  transfer curves.

## **III. RESULTS AND DISCUSSION**

## A. I-V and initial behavior

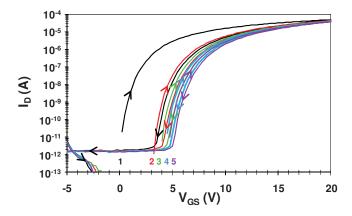

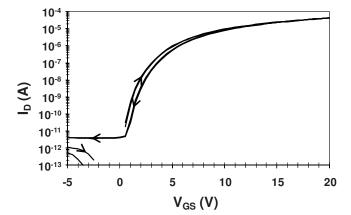

Representative  $I_D$ - $V_{GS}$  transfer curves of ZTO TFTs with either (a) a 200 nm Al<sub>2</sub>O<sub>3</sub> gate dielectric or (b) a 100 nm PECVD  $SiO_2$  gate dielectric are shown in Fig. 2. The gate capacitance of both device types was roughly equivalent. For both devices, the ZTO channel was deposited at 75 W of rf power. The ZTO TFTs with the Al<sub>2</sub>O<sub>3</sub> gate dielectric showed S = 0.38 V/dec, $I_{\rm ON}/I_{\rm OFF} = \sim 10^7$ , and  $\mu_{\rm inc}({\rm max})$ =13.3  $\text{cm}^2/\text{V}$  s. Comparable performance was observed for PECVD SiO<sub>2</sub> gate dielectric devices with S=0.35 V/dec,  $I_{\rm ON}/I_{\rm OFF}$  = ~10<sup>7</sup>, and  $\mu_{\rm inc}({\rm max})$  = 18.3 cm<sup>2</sup>/V s. Although the S values for Al<sub>2</sub>O<sub>3</sub> dielectric and SiO<sub>2</sub> dielectric TFTs are similar (due to having similar maximum  $I_D$ - $V_{GS}$  slopes), the slope of the  $I_D$ - $V_{GS}$  curve of the SiO<sub>2</sub> devices remains steep over a wider voltage range than that of the Al<sub>2</sub>O<sub>3</sub> devices, resulting in a sharper overall turn-on and suggesting that the overall trap density at the SiO<sub>2</sub>/ZTO interface is lower than that of the Al<sub>2</sub>O<sub>3</sub>/ZTO interface. It is typically observed, but not widely reported, that AOS TFTs require several I-V sweeps before operation is stabilized. It can, therefore, be misleading to report only the first  $V_{GS}$  sweep. To give a realistic picture of device operation, the initial set of five se-

FIG. 2. (Color online)  $I_D/V_{GS}$  transfer curves (the initial five sweeps are shown in different colors and numbered sequentially) for ZTO TFTs with either (a) an ALD Al<sub>2</sub>O<sub>3</sub> or (b) a PECVD SiO<sub>2</sub> bottom-gate dielectric. The arrows indicate the sweep direction.

quential double-sweep  $I_D$ - $V_{GS}$  curves ( $V_{GS}$  swept from -5 to +20 V and then back to -5 V) is shown for each device. For both Al<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub> gate dielectric devices, a positive  $V_{ON}$  shift is observed during the initial double-sweeps. By the fifth double-sweep, the large initial clockwise hysteresis has stabilized at approximately 0.30 V for the SiO<sub>2</sub> devices and 0.50 V for the Al<sub>2</sub>O<sub>3</sub> devices. In both cases, the curves are shifted roughly parallel, with negligible change in mobility and *S*, suggesting that the shift is due primarily to charge trapping. The PECVD SiO<sub>2</sub> devices exhibit much less shift;  $\Delta V_{ON}$  is less than 0.5 V in the first five sweeps compared to a  $\Delta V_{ON}$  of approximately 4.5 V for the Al<sub>2</sub>O<sub>3</sub> devices. Upon the removal of bias, complete recovery of  $V_{ON}$  is observed within 36 h at room temperature.

The observation of clockwise hysteresis is consistent with trapping and detrapping of electrons in traps near the interface,<sup>26,27</sup> while the positive  $V_{ON}$  shift suggests trapping of electrons further from the interface. The parallel nature of the shift (no significant change in *S* or mobility) combined with room temperature recovery of  $V_{ON}$  after stressing suggests that defect creation is not occurring.<sup>20,28</sup> Since the only difference between the PECVD SiO<sub>2</sub> and ALD Al<sub>2</sub>O<sub>3</sub> de-

# J. Vac. Sci. Technol. B, Vol. 28, No. 4, Jul/Aug 2010

FIG. 3. (Color online)  $I_D/V_{GS}$  transfer curves (the initial five sweeps are shown in different colors and numbered sequentially) of ZTO TFTs with ALD Al<sub>2</sub>O<sub>3</sub> deposited at 300 °C. The arrows indicate the sweep direction.

vices is the gate dielectric, the location of the trapping is suspected to be either at the ZTO/dielectric interface or within the dielectric itself.

Charge trapping-related bias stress instabilities have also been reported in a variety of AOS channel/insulator combinations.<sup>9,20,21,23,26,28,29</sup> Positive bias instabilities in IGZO TFTs with SiO<sub>2</sub> dielectrics have been attributed to traps both in the channel<sup>26</sup> and in the interface/bulk dielectric.<sup>9</sup> Parallel positive transfer curve shifts have been attributed to charge trapping in bulk dielectric defects in ZTO channel TFTs with ALD ATO gate dielectrics<sup>20</sup> and to charge trapping at the channel/dielectric interface in spin coated thermal SiO<sub>2</sub>/ZTO TFTs.<sup>21</sup> Gorrn *et al.*<sup>20</sup> reported that the stoichiometry of the ZTO channel deposited via plasma assisted pulsed laser deposition has a large influence on the bias stability of ZTO/ATO TFTs. The  $\Delta V_{ON}$  of our devices are qualitatively consistent with the reported bias stress behavior of the ZTO TFTs of Gorrn *et al.* with similar stoichiometry (~2:1 Zn:Sn ratio) but different gate dielectric.

There are several other potential process-related causes for the electrical instabilities observed in these bottom-gate TFTs, including the condition of the bottom-gate dielectric surface prior to channel deposition, details of the dielectric deposition process, and plasma damage of the gate dielectric during channel deposition. The underlying substrate can often exert an influence on the crystal structure of an overlying deposited thin film.<sup>30</sup> However, x-ray diffraction (not shown) of ZTO films deposited on both Al<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub> showed the films to be amorphous and unchanged by the underlying material. In an effort to improve bias stress stability of the Al<sub>2</sub>O<sub>3</sub> devices and determine the origin of charge trapping, the influence of (i) ALD temperature and (ii) plasma damage of the Al<sub>2</sub>O<sub>3</sub> was investigated.

It is known that ALD temperature can have a significant effect on the electrical and physical properties of insulators.<sup>31–33</sup> To investigate the impact of Al<sub>2</sub>O<sub>3</sub> ALD temperature on stability, ZTO TFTs were prepared with Al<sub>2</sub>O<sub>3</sub> dielectrics deposited at either 200 or 300 °C. The first five double-sweep  $I_D$ - $V_{GS}$  transfer curves for a representative 300 °C Al<sub>2</sub>O<sub>3</sub> device are shown in Fig. 3 [the 200 °C Al<sub>2</sub>O<sub>3</sub>

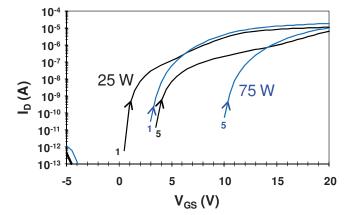

FIG. 4. (Color online) Plot of first and fifth  $I_D/V_{GS}$  sweeps for Al<sub>2</sub>O<sub>3</sub>/ZTO TFTs with the ZTO channel deposited at either 75 W (blue) or 25 W (black) of rf power. The arrows indicate the sweep direction. Only the positive sweep direction is shown.

device is shown in Fig. 2(a)]. For the 300 °C device, S = 0.31 V/dec,  $\mu_{\text{inc}}(\text{max}) = 14.5 \text{ cm}^2/\text{V}$  s, and an  $I_{\text{ON}}/I_{\text{OFF}}$  of approximately 10<sup>7</sup> was extracted. In both the 200 and 300 °C devices, a positive parallel  $V_{\text{ON}}$  shift is observed with each subsequent trace along with a large initial clockwise hysteresis that stabilizes by the fifth sweep at approximately 0.50 V. This close similarity between the two device types indicates that variation of ALD temperature over the range of 200–300 °C does not exert a strong influence on ZTO/Al<sub>2</sub>O<sub>3</sub> interface quality, device performance, or device stability.

In SBG TFTs, the gate dielectric is exposed to plasma during rf sputter deposition of the AOS channel (see crosssection in Fig. 1). It is well known that plasma exposure can degrade the electrical properties of gate dielectrics.<sup>34</sup> Oh et al.<sup>10</sup> showed that in ZnO-channel bottom-gate TFTs, exposure of the Al<sub>2</sub>O<sub>3</sub> dielectric to plasma during rf sputter channel deposition resulted in degradation of the channel/ dielectric interface and increased electron-trapping-related bias instabilities. To investigate the effect of plasma exposure on the bias stress stability, ZTO/Al<sub>2</sub>O<sub>3</sub> SBG TFTs were fabricated with ZTO sputter deposition performed at two different levels of rf power. Shown in Fig. 4 are the  $I_D$ - $V_{GS}$  transfer curves for TFTs with the ZTO channel deposited at either (a) 75 W or (b) 25 W of rf power. Once again, devices were characterized using a sequential series of five double-sweep  $I_D$ - $V_{GS}$  transfer curves. For clarity, only the -5 to 25 V positive sweeps for only the first and fifth transfer curves are shown. As expected, when the power was reduced from 75 to 25 W, the positive  $\Delta V_{\rm ON}$  between the first and fifth gate voltage sweeps was reduced by approximately one-half (from  $\sim 7$  to  $\sim 3$  V). The initial  $V_{\rm ON}$  shift of the 25 W devices was shifted negatively 25 W compared to that of the 75 W devices (from 3 to 0.5 V). Clockwise hysteresis was slightly reduced from 0.65 to 0.55 V. This result indicates that plasma exposure of the Al<sub>2</sub>O<sub>3</sub> during rf sputter deposition of the ZTO channel plays a role in bias instability. However, mobility is degraded, the  $I_D$ - $V_{GS}$  response is "kinked," and although  $\Delta V_{\rm ON}$  is reduced, it is not eliminated in the low

#### JVST B - Microelectronics and Nanometer Structures

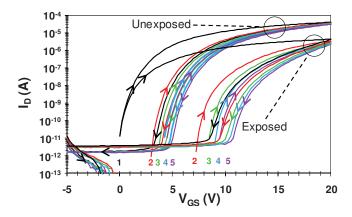

FIG. 5. (Color online) Plot of  $I_D$  vs  $V_{GS}$  for ZTO TFTs with the bottom Al<sub>2</sub>O<sub>3</sub> gate dielectric either left unexposed or exposed to O<sub>2</sub> plasma prior to channel deposition. The initial five sweeps are shown in different colors and numbered sequentially. The arrows indicate the sweep direction.

rf power (25 W) TFTs. Thus, reduced RF power alone is not a viable strategy for improving overall TFT performance.

To further investigate the effect of plasma exposure, TFTs with identical Al<sub>2</sub>O<sub>3</sub> dielectrics were exposed to additional O<sub>2</sub> plasma just prior to rf sputtering of the ZTO channel and compared to devices that did not receive the O<sub>2</sub> plasma exposure. The additional O<sub>2</sub> plasma exposure duration was 3 min at 75 W power [20 SCCM (SCCM denotes cubic centimeter per minute at STP) O<sub>2</sub> flow, 20 mTorr pressure]. The initial five double-sweep  $I_D$ - $V_{GS}$  transfer curves for the unexposed and O<sub>2</sub> plasma-exposed devices are shown in Fig. 5. The O<sub>2</sub> plasma-exposed devices displayed increased  $\Delta V_{ON}$  (4.5–10.5 V), degraded mobility, and lower  $I_{ON}/I_{OFF}$ , providing further evidence that plasma exposure of the bottom Al<sub>2</sub>O<sub>3</sub> dielectric plays a role in the bias instability.

The initial five  $I_D$ - $V_{GS}$  sweeps for the ZTO SBG TFTs investigated in this work are characterized by a rigid positive  $V_{\rm ON}$  shift. As seen in Fig. 2, ZTO TFTs with PECVD SiO<sub>2</sub> gate dielectrics are more stable than devices with ALD Al<sub>2</sub>O<sub>3</sub> gate dielectrics. Because the only difference between the two devices is the bottom-gate dielectric, additional electron trapping either at the  $Al_2O_3/ZTO$  interface or in the  $Al_2O_3$  is implicated. Data in Figs. 4 and 5 indicate that plasma exposure of the  $Al_2O_3$  is detrimental. However, the PECVD SiO<sub>2</sub>/ZTO interface appears better able to withstand the plasma exposure during channel deposition. In an effort to combine the interface quality of the PECVD SiO<sub>2</sub> with the higher dielectric constant of Al<sub>2</sub>O<sub>3</sub>, a combination of the two materials was used. The 200 nm ALD Al2O3 dielectric was capped with a thin ( $\sim 2-5$  nm) layer of PECVD SiO<sub>2</sub> prior to ZTO channel deposition. The transfer characteristics (for clarity, only first and fifth double  $V_{GS}$  sweeps are shown) of this Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> "capped"/ZTO device are shown in Fig. 6. Although 0.5 V clockwise hysteresis is still present, the shift in  $V_{\rm ON}$  during the initial five  $I_D - V_{GS}$  double-sweeps appears negligible. The device parameters of the Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> "cap"/ ZTO devices are similar to uncapped  $Al_2O_3$  devices: S =0.46 V/dec,  $I_{\rm ON}/I_{\rm OFF} = \sim 10^7$ , and  $\mu_{\rm inc}({\rm max})$ =12.2 cm<sup>2</sup>/V s. The fact that the thin SiO<sub>2</sub> capping layer

FIG. 6. Plot of  $I_D$  vs  $V_{GS}$  (the first and fifth double-sweeps are shown) for ZTO TFTs with SiO<sub>2</sub>-capped Al<sub>2</sub>O<sub>3</sub> gate dielectrics. The arrows indicate the sweep direction.

effectively suppresses  $V_{ON}$  shift during initial transfer curve measurements strongly suggests that electron trapping at or very near the channel/Al<sub>2</sub>O<sub>3</sub> interface dominates.

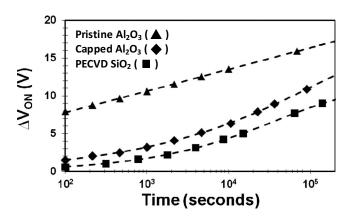

### B. Bias stressing

To further investigate the source of the  $V_{ON}$  instability, ZTO TFTs with ALD Al2O3, PECVD SiO2, and PECVD SiO<sub>2</sub>-capped Al<sub>2</sub>O<sub>3</sub> gate dielectrics were subjected to extend positive bias stressing. Bias stressing was performed in the dark at room temperature in atmosphere with  $V_{GS}$ =+20 V and  $V_{DS}$ =+1 V, with stress interrupted at approximately logarithmic time intervals to measure  $I_D$ - $V_{GS}$  transfer curves.  $\Delta V_{\rm ON}$  is defined as the cumulative change in  $V_{\rm ON}$  between the initial (unstressed) transfer curve and poststress transfer curve. Analysis of  $\Delta V_{\rm ON}$  versus time is performed using trapping models. A semilog plot of  $\Delta V_{ON}$  versus stress time for SBG ZTO TFTs with either ALD Al<sub>2</sub>O<sub>3</sub>, PECVD SiO<sub>2</sub>, or PECVD SiO<sub>2</sub>-capped Al<sub>2</sub>O<sub>3</sub> gate dielectrics is shown in Fig. 7. For all devices,  $\Delta V_{\rm ON}$  is positive. Upon the removal of the bias voltage, full  $V_{\rm ON}$  recovery was observed after 36 h in the dark at room temperature. For the Al<sub>2</sub>O<sub>3</sub> dielectric devices,  $\Delta V_{\rm ON}$  exhibits a clear logarithmic dependence on stress time,

FIG. 7. Semilog plot of  $\Delta V_{ON}$  vs stress time for ZTO TFTs with either ALD Al<sub>2</sub>O<sub>3</sub>, PECVD SiO<sub>2</sub>, or SiO<sub>2</sub>-capped Al<sub>2</sub>O<sub>3</sub> gate dielectrics. The dashed lines show the model fits.

# J. Vac. Sci. Technol. B, Vol. 28, No. 4, Jul/Aug 2010

indicative of trapping at pre-existing defects with a single capture cross-section, without creation of new defects.<sup>35</sup>

In contrast with the Al<sub>2</sub>O<sub>3</sub>/ZTO devices, positive bias stressing of the SiO<sub>2</sub>/ZTO devices showed a smaller  $\Delta V_{ON}$ over the 10<sup>5</sup> s time period and exhibited a nonlogarithmic dependence on stress time. Instead,  $\Delta V_{ON}$  for these devices can be well described by the stretched-exponential model that was originally developed to model bias instabilities in *a*-Si:H,<sup>36</sup> and later used to model trapping in high dielectric constant oxides<sup>37</sup> defined by

$$\Delta V_{\rm ON} = \Delta V_{\rm ON0} \{1 - \exp[-(t/\tau)^{\beta}]\},\tag{2}$$

where  $\beta$  is the stretching exponent,  $\tau$  is the characteristic time constant for trap redistribution, and  $\Delta V_{ON0}$  is the saturation voltage shift, which is asymptotically approached at very long stress times. (Note that since the transfer curves shift rigidly with bias stress,  $\Delta V_{ON}$  can be substituted for  $\Delta V_{\text{th}}$  in the original formulation of the stretched-exponential model.) For the PECVD SiO<sub>2</sub> dielectric devices, a fit to Eq. (2) yields  $\beta$ =0.47,  $\tau$ =3.9×10<sup>5</sup> s, and  $V_{ON0}$ =10.7 V.

Similar to the PECVD SiO<sub>2</sub> devices,  $\Delta V_{ON}$  for the SiO<sub>2</sub>-capped Al<sub>2</sub>O<sub>3</sub>/ZTO TFTs also shows a nonlogarithmic dependence on stress time that can be modeled well by a stretched-exponential time dependence. In this case, fitting  $\Delta V_{ON}$  to Eq. (2) yields  $\beta$ =0.34,  $\tau$ =1.2×10<sup>5</sup>, and  $V_{ON0}$  = 18.4. It is apparent from Fig. 7 that the SiO<sub>2</sub> capping layer not only increases stability but also strongly influences the trapping behavior, with the SiO<sub>2</sub>-capped Al<sub>2</sub>O<sub>3</sub> gate dielectric devices more closely resembling PECVD SiO<sub>2</sub> devices rather than the Al<sub>2</sub>O<sub>3</sub> devices. The similarity between the SiO<sub>2</sub> and the SiO<sub>2</sub>-capped devices further suggests that the near-interfacial area dominates trapping in these ZTO devices. Based on the lower magnitude of  $\Delta V_{ON}$  in SiO<sub>2</sub> and SiO<sub>2</sub>-capped TFTs, the trap density is inferred to be lower than that of Al<sub>2</sub>O<sub>3</sub>.

As developed for a-Si:H TFTs,<sup>36</sup> the stretchedexponential model assumes that there is negligible stressinduced defect creation in the channel or at the interface. Libsch and Kanicki<sup>36</sup> interpreted the exponent term,  $\beta$ , to relate to the energy barrier to charge redistribution-the movement of charge at long stress times from shallow to deeper traps. Zafar et al.<sup>37</sup> developed a model for charge trapping in metal/oxide/semiconductor (MOS) devices with high-k dielectrics which results in the same stretchedexponential equation, but in this case  $\beta$  is interpreted to relate to the width of the distribution of the electron trap capture cross sections. The stretched-exponential equation has been also used to model trapping in several AOS device structures.<sup>9,11,12</sup> Lee et al.<sup>12</sup> investigated rf sputtered IGZO TFTs with ALD  $Al_2O_3$  dielectrics with or without a  $SiN_X$ capping layer. In interesting contrast to our devices, their TFTs with uncapped dielectrics were found to be modeled well by the stretched-exponential equation. Conversely, when the TFT dielectric was capped with  $SiN_X$ , the bias stability worsened and  $\Delta V_{\rm ON}$  became logarithmic with time. It was concluded that the Al2O3 dielectric allowed a redistribution of trapped electrons-hence the fit to the stretchedexponential equation—while the capping layer restricted redistribution but had a higher interface trap density.

In this work, the time dependence of the positive bias stress-induced  $V_{ON}$  shift is logarithmic for the Al<sub>2</sub>O<sub>3</sub>/ZTO devices, suggesting trapping at pre-existing defects with a single capture cross-section without creation of new defects. The fact that the addition of a thin interfacial capping layer of PECVD SiO<sub>2</sub> between the Al<sub>2</sub>O<sub>3</sub> and the ZTO channel dramatically changes the time dependence of the  $V_{\rm ON}$  shift is a strong indication that the interface dominates the positive bias stress response. The close fit of the stretchedexponential model to the SiO<sub>2</sub>/ZTO and Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>-cap/ZTO devices may be interpreted to point to either (i) a redistribution of the trapped charge to deeper states in the SiO<sub>2</sub> (and in the capped devices, the  $Al_2O_3$ layer) or (ii) the presence of a distribution of trap capture cross sections in PECVD SiO<sub>2</sub> layers. Note, however, that Eq. (2) can be arrived at with very different assumptions about defect behavior.<sup>36,37</sup> Without the benefit of additional information about point defects such as that provided by electron spin resonance,<sup>38,39</sup> attaching a specific physical meaning to  $\beta$  is not straightforward.

## **IV. CONCLUSION**

rf sputtered ZTO channel SBG TFTs were fabricated with either ALD Al2O3, PECVD SiO2, or PECVD SiO2-capped Al<sub>2</sub>O<sub>3</sub> gate dielectrics. The initial operational stability was compared using the first five double  $I_D$ - $V_{GS}$  sweeps. All devices exhibited clockwise hysteresis and a parallel positive shift of the transfer curve during these initial five sweeps with little change in S or mobility, consistent with electron trapping and detrapping at existing defects with little or no creation of new defects. TFTs with an ALD Al<sub>2</sub>O<sub>3</sub> dielectric exhibited greater  $V_{ON}$  shift than devices with a PECVD SiO<sub>2</sub> dielectric. Increasing the ALD temperature of Al<sub>2</sub>O<sub>3</sub> was found to have little influence on the bias instability. On the other hand, exposure of the Al<sub>2</sub>O<sub>3</sub> to O<sub>2</sub> plasma degraded both performance and stability, indicating that plasma damage during channel deposition in these SBG TFTs is an important consideration. Decreasing the rf sputtering power during ZTO deposition reduced  $V_{ON}$  shift, but resulted in degraded device properties. Protecting the Al<sub>2</sub>O<sub>3</sub> from plasma exposure through the addition of a thin ( $\sim 3$  nm) interfacial capping layer between the Al<sub>2</sub>O<sub>3</sub> and the ZTO channel was found to greatly improve device stability.

Constant positive bias stressing revealed a logarithmic time dependence of  $V_{\rm ON}$  shift in the Al<sub>2</sub>O<sub>3</sub>/ZTO devices (indicative of trapping at pre-existing defects with a single small capture cross section<sup>35</sup>) but a stretched-exponential time dependence in the SiO<sub>2</sub>/ZTO devices. The stretched-exponential time dependence may be interpreted as either a distribution of capture cross sections<sup>30</sup> or redistribution over time of trapped charge into deeper traps.<sup>29</sup> Both the logarithmic and stretched-exponential models are also consistent with little or no creation of new defects. Addition of a thin (~2–5 nm) layer of PECVD SiO<sub>2</sub> between the Al<sub>2</sub>O<sub>3</sub> and ZTO channel was sufficient to reduce trapping and dramati-

cally alter the time dependence of the trapping behavior from logarithmic to stretched exponential. Upon the removal of the bias voltage, full recovery of  $V_{\rm ON}$  is observed in all devices after 36 h in the dark at room temperature.

Overall, the observation of positive bias induced rigid positive  $V_{\rm ON}$  shifts with a strong dependence on the details of the ZTO/dielectric interface accompanied by little change in *S* and mobility, and full recovery of  $V_{\rm ON}$  at room temperature suggests that the bias stability of these SBG ZTO channel TFTs is dominated by electron trapping at the ZTO/dielectric interface or in the dielectric near the interface without significant creation of new defects. Optimization of the ZTO/ dielectric interface will be critical for high performance and stable long-term operation. It is likely that a top gate device structure would improve the performance and stability of ZTO/Al<sub>2</sub>O<sub>3</sub> TFTs by avoiding exposure of the dielectric surface to plasma during deposition of the channel.

# ACKNOWLEDGMENTS

The authors gratefully acknowledge the support of the National Science Foundation through Grant No. DMR-0805372 and a REU supplement as well as matching fund support from the Oregon Nanoscience and Microtechnologies Institute (ONAMI).

- <sup>1</sup>K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, Nature (London) **432**, 488 (2004).

- <sup>2</sup>R. L. Hoffman, B. J. Norris, and J. F. Wager, Appl. Phys. Lett. **82**, 733 (2003).

- <sup>3</sup>P. F. Carcia, R. S. McLean, M. H. Reilly, and J. G. Nunes, Appl. Phys. Lett. **82**, 1117 (2003).

- <sup>4</sup>S. Masuda, K. Kitamura, Y. Okumura, S. Miyatake, H. Tabata, and T. Kawai, J. Appl. Phys. **93**, 1624 (2003).

- <sup>5</sup>P. Görrn, F. Ghaffari, T. Riedl, and W. Kowalsky, Solid-State Electron. **53**, 329 (2009).

- <sup>6</sup>H.-Q. Chiang, J. F. Wager, R. L. Hoffman, J. Jeong, and D. A. Keszler, Appl. Phys. Lett. **86**, 013503 (2005).

- <sup>7</sup>J. B. Kim, C. Fuentes-Hernandez, W. J. Potscavage, Jr., X.-H. Zhang, and B. Kippelen, Appl. Phys. Lett. **94**, 142107 (2009).

- <sup>8</sup>P. F. Carcia, R. S. McLean, and M. H. Reilly, Appl. Phys. Lett. **88**, 123509 (2006).

- <sup>9</sup>J.-M. Lee, I.-T. Cho, J.-H. Lee, and H.-I. Kwon, Appl. Phys. Lett. **93**, 093504 (2008).

- <sup>10</sup>M. S. Oh, K. Lee, J. H. Song, B. H. Lee, M. M. Sung, D. K. Hwang, and

- S. Im, J. Electrochem. Soc. 155, H1009 (2008).

- <sup>11</sup>K. Nomura, T. Kamiya, M. Hirano, and H. Hosono, Appl. Phys. Lett. 95, 013502 (2009).

- <sup>12</sup>J.-M. Lee, I.-T. Cho, J.-H. Lee, W.-S. Cheong, C.-S. Hwang, and H.-I. Kwon, Appl. Phys. Lett. **94**, 222112 (2009).

- <sup>13</sup>S.-H. K. Park et al., ETRI J. **31**, 653 (2009).

- <sup>14</sup>K. Song, D. Kim, X.-S. Li, T. Jun, Y. Jeong, and J. Moon, J. Mater. Chem. 19, 8881 (2009).

- <sup>15</sup>M. Powell, C. Vanberkel, and J. Hughes, Appl. Phys. Lett. **54**, 1323 (1989).

- <sup>16</sup>H. Kavak and H. Shanks, Solid-State Electron. **49**, 578 (2005).

- <sup>17</sup>D. L. Staebler and C. R. Wronski, Appl. Phys. Lett. **31**, 292 (1977).

- <sup>18</sup>D. R. Allee *et al.*, IEEE Trans. Electron Devices **56**, 1166 (2009).

- <sup>19</sup>J. Robertson, Thin Solid Films **516**, 1419 (2008).

- <sup>20</sup>P. Görrn, P. Hölzer, T. Riedl, W. Kowalsky, J. Wang, T. Weimann, P. Hinze, and S. Kipp, Appl. Phys. Lett. **90**, 063502 (2007).

- <sup>21</sup>S.-J. Seo, C. G. Choi, Y. H. Hwang, and B.-S. Bae, J. Phys. D: Appl. Phys. 42, 035106 (2009).

- <sup>22</sup>W. S. Cheong, S. M. Yoon, J. H. Shin, and C. S. Hwang, J. Korean Phys. Soc. 54, 544 (2009).

- <sup>23</sup>Y. Jeong, K. Song, D. Kim, C. Y. Koo, and J. Moon, J. Electrochem. Soc. 156, H808 (2009).

- <sup>24</sup>J. F. Wager, D. A. Keszler, and R. E. Presley, *Transparent Electronics* (Springer, New York, 2008), Chap. 5.

- <sup>25</sup>R. Hoffman, J. Appl. Phys. **95**, 5813 (2004).

- <sup>26</sup>K. Hoshino, D. Hong, H. Q. Chiang, and J. F. Wager, IEEE Trans. Electron Devices 56, 1365 (2009).

- <sup>27</sup>See, for example, T. R. Oldham, *Ionizing Radiation Effects in MOS Devices* (World Scientific, Singapore, 1999), Chap. 2.

- <sup>28</sup>R. Cross and M. De Souza, IEEE Trans. Device Mater. Reliab. 8, 277 (2008).

- <sup>29</sup>J. F. Conley, Jr., "Instabilities in amorphous oxide semiconductor thin film transistors," IEEE Trans. Device Mater. Reliab. (in press).

- <sup>30</sup>Y. Gao, S. He, P. Alluri, M. Engelhard, A. S. Lea, J. Finder, B. Melnick, and R. L. Hance, J. Appl. Phys. 87, 124 (2000).

- <sup>31</sup>M.-Y. Li, Y.-Y. Chang, H.-C. Wu, C.-S. Huang, J.-C. Chen, J.-L. Lue, and S.-M. Chang, J. Electrochem. Soc. **154**, H967 (2007).

- <sup>32</sup>M. D. Groner, F. H. Fabreguette, J. W. Elam, and S. M. George, Chem. Mater. **16**, 639 (2004).

- <sup>33</sup>J. L. van Hemmen, S. B. S. Heil, J. H. Klootwijk, F. Roozeboom, C. J. Hodson, M. C. M. van de Sanden, and W. M. M. Kessels, J. Electrochem. Soc. **154**, G165 (2007).

- <sup>34</sup>A. Martin, J. Vac. Sci. Technol. B **27**, 426 (2009).

- <sup>35</sup>T. H. Ning and H. N. Yu, J. Appl. Phys. **45**, 5373 (1974).

- <sup>36</sup>F. R. Libsch and J. Kanicki, Appl. Phys. Lett. **62**, 1286 (1993).

- <sup>37</sup>S. Zafar, A. Callegari, E. Gusev, and M. V. Fischetti, J. Appl. Phys. **93**, 9298 (2003).

- <sup>38</sup>P. M. Lenahan and J. F. Conley, Jr., J. Vac. Sci. Technol. B 16, 2134 (1998).

- <sup>39</sup>P. M. Lenahan and J. F. Conley, Jr., IEEE Trans. Device Mater. Reliab. 5, 90 (2005).